Understanding New Chip Technologies: Chiplets Explained, 3D Packaging, and Advanced Semiconductor Nodes

Estimated reading time: 12 minutes

Key Takeaways

- The semiconductor industry is shifting from monolithic to modular architectures with chiplets, 3D packaging, and advanced semiconductor nodes.

- Chiplets enable flexible, cost-effective chip assembly by combining specialized smaller dies rather than one large monolithic chip.

- 3D packaging vertically stacks dies for better performance, smaller footprint, and power efficiency but presents engineering challenges.

- Advanced semiconductor nodes represent smaller transistor feature sizes improving performance but are costly and complex to manufacture.

- These technologies synergize to overcome limits of Moore’s Law, driving innovation for AI, edge computing, and power-efficient devices.

- Understanding these trends is critical for staying ahead in the semiconductor landscape as the market moves toward $1 trillion by 2030.

Table of contents

- Overview of New Chip Technologies: Modular, Scalable, and Cost-Effective Design

- Chiplets Explained: Modular Building Blocks of Future Chips

- 3D Packaging: Vertical Integration Transforming Chip Design

- Advanced Semiconductor Nodes: The Race to the Smallest Features

- The Future Outlook of New Chip Technologies: Innovation and Expansion

- Conclusion: The Integrated Path Forward for New Chip Technologies

- Frequently Asked Questions

The semiconductor world is rapidly evolving thanks to new chip technologies. These cutting-edge advances are reshaping how chips are designed, made, and used. This change is driven by booming demands in artificial intelligence (AI), edge computing, and the need for power-efficient devices. Traditional methods, once guided by Moore’s Law—the doubling of transistor density every two years—are now reaching physical and economic limits. To keep pace, the industry is turning to modular designs known as chiplets, vertical stacking through 3D packaging, and cutting-edge manufacturing on advanced semiconductor nodes.

In this blog, we will explore these three key innovations:

- Chiplets explained: What they are and why they matter.

- 3D packaging: How vertical stacking transforms device design.

- Advanced semiconductor nodes: The role of smaller process geometries.

Together, these new chip technologies promise to drive the next wave of semiconductor innovation in a rapidly changing landscape where performance, efficiency, and cost dictate future success. The semiconductor industry is evolving at an unprecedented pace, opening doors to possibilities never before imagined.

For an in-depth view on these trends and their impact, see the detailed analysis from Jama Software’s 2026 semiconductor predictions: https://www.jamasoftware.com/blog/2026-predictions-for-semiconductors-ai-chiplets-and-the-path-to-sustainable-innovation/

Also, explore the broader future of technology to understand how these chip innovations fit into the bigger picture:

https://techcirclenow.com/future-of-technology-2030

Overview of New Chip Technologies: Modular, Scalable, and Cost-Effective Design

New chip technologies mark a major shift away from traditional monolithic chip design. Instead of building single large dies combining all functions, today’s innovation focuses on modular, disaggregated, and vertically integrated chip architectures. This paradigm shift addresses three critical challenges facing the semiconductor industry:

Performance and Scalability

Moore’s Law, which fueled decades of growth, is slowing due to physical limits in transistor miniaturization. To continue improving performance, chipmakers are turning to new architectures like chiplets—collections of smaller, specialized dies—and 3D packaging, which stacks chips vertically. These approaches help maintain consistent gains in performance and scalability despite the plateauing of traditional node shrinking.

For context on semiconductor industry innovation and performance benchmarks, see: https://techcirclenow.com/semiconductor-trends-driving-innovation

Power Efficiency

Power consumption is a key limitation for modern devices, especially those relying on edge AI and local processing. New chips need to be optimized for energy-efficiency to operate in battery-powered and distributed environments. These new chip technologies facilitate specialized designs like low-power accelerators and sensor-integrated chips that drastically reduce energy use while boosting performance.

Learn more about AI-driven advances influencing power-efficient designs here: https://techcirclenow.com/latest-ai-trends-2025-updates

Manufacturing Economics

Moving to smaller semiconductor nodes has become exponentially expensive. Building an entire chip at the latest 3nm or below node is costly and complex. Chiplets allow semiconductor companies to strategically combine components fabricated on different, optimized nodes. For example, compute-intensive chiplets can use the latest advanced nodes, while I/O or memory chiplets leverage more mature, less expensive nodes. This approach cuts overall manufacturing costs without sacrificing performance.

For a detailed look into semiconductor manufacturing processes and challenges, check: https://techcirclenow.com/semiconductor-manufacturing-process-explained

Market Impact

The semiconductor market is forecasted to hit $1 trillion in annual revenue by 2030, largely fueled by these new chip technologies rather than relying solely on traditional transistor scaling. This modular, vertically integrated approach is critical for the industry to sustain growth in the next decade.

For further insights on strategic semiconductor shifts, see Jama Software’s predictions here: https://www.jamasoftware.com/blog/2026-predictions-for-semiconductors-ai-chiplets-and-the-path-to-sustainable-innovation/

Chiplets Explained: Modular Building Blocks of Future Chips

What Are Chiplets?

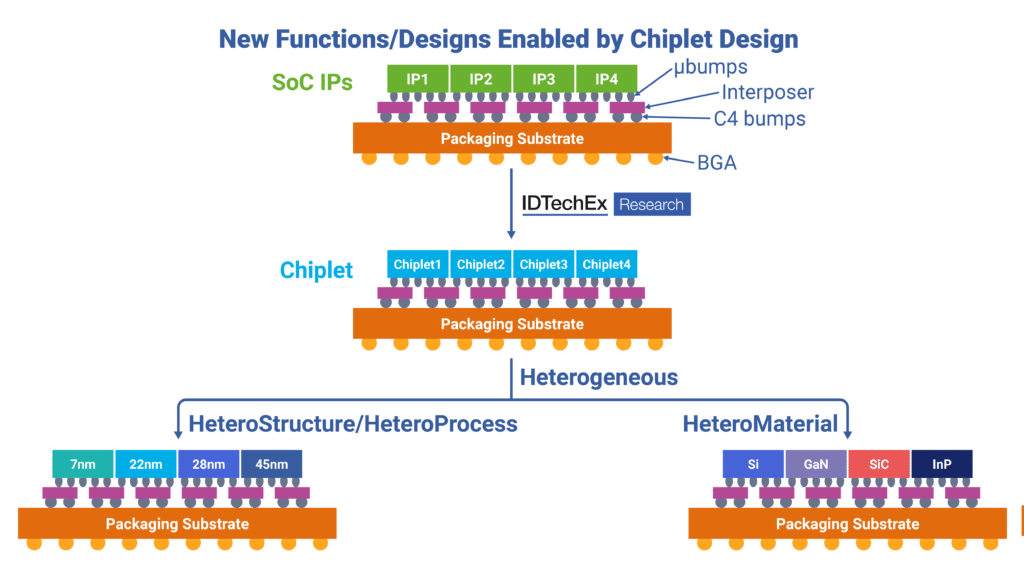

Chiplets are smaller, specialized semiconductor dies designed separately and then integrated into a larger single chip package. This contrasts with traditional monolithic chips where all functions—processing cores, memory, I/O—are fabricated on one large silicon die.

Modularity and Function Specialization

Each chiplet focuses on a specific task:

- Compute chiplets optimized for high-speed operation.

- Memory chiplets designed for fast access and storage.

- I/O chiplets handling communications, sensors, or connectivity.

This modularity enables manufacturers to optimize each chiplet for speed, power, or cost independently.

Advantages of Chiplets

- Mixed Process Nodes: Critical chiplets like processors can be manufactured on advanced semiconductor nodes (e.g., 3nm), while supporting chiplets can be made on mature, less costly nodes (e.g., 7nm or 14nm).

- Improved Yields: Smaller die sizes yield better manufacturing success rates, reducing waste and lowering costs.

- Cost-Effectiveness: Reusing proven chiplet designs across products and sourcing parts from different suppliers reduces development time and expense.

- Customization: Enables rapid assembly of application-specific chips tailored to particular workloads or markets.

Industry Impact and Challenges

Chiplets are indispensable to achieving the industry’s ambitious growth targets. Without chiplet architectures, the high costs and yield risks of large monolithic chips would stifle progress.

However, chiplets introduce new engineering challenges:

- High-speed interconnects between chiplets require advanced packaging technology.

- Thermal management becomes more complex due to heat from multiple dies.

- Coordinating multi-supplier supply chains adds logistical complexity.

Despite these obstacles, chiplets are a foundational element of new chip technologies, unlocking scalable, adaptable semiconductor solutions.

More about chiplets and their importance is available here: https://www.jamasoftware.com/blog/2026-predictions-for-semiconductors-ai-chiplets-and-the-path-to-sustainable-innovation/

3D Packaging: Vertical Integration Transforming Chip Design

What Is 3D Packaging?

3D packaging refers to stacking multiple semiconductor dies vertically within a single package. Instead of placing chips side-by-side on a flat substrate, dies are layered on top of each other using sophisticated interconnect technologies such as micro-bumps and silicon interposers.

Technical Overview

- Dies are fabricated separately.

- Vertical stacking is achieved via precise alignment and connection using micro-bumps or through-silicon vias (TSVs).

- Interposers act as intermediate connection layers enabling dense wiring between stacked dies.

Benefits of 3D Packaging

- Enhanced Speed: Short inter-layer distances drastically reduce signal latency and improve timing margins.

- Reduced Physical Footprint: Devices can become physically smaller but more functionally rich—critical for wearables, mobile, and compact edge devices.

- Lower Power Consumption: Shorter connection paths reduce power loss during data transmission, increasing energy efficiency.

Challenges in 3D Packaging

- Managing heat buildup in stacked layers is difficult and requires innovative thermal solutions.

- Achieving precise alignment and manufacturing yield at scale requires advancing current fabrication processes.

- Cost and complexity in manufacturing must improve for widespread adoption beyond premium devices.

3D packaging complements both chiplet designs and advanced nodes by integrating heterogeneous components vertically, maximizing density regardless of process node size.

For an in-depth look at 3D packaging advances, visit Pragmatic Semiconductor’s insights: https://www.pragmaticsemi.com/semiconductor-technology-trends-and-predictions-2026/

Advanced Semiconductor Nodes: The Race to the Smallest Features

What Are Advanced Semiconductor Nodes?

Advanced semiconductor nodes indicate fabrication processes measured in nanometers (e.g., 5nm, 3nm). They define the smallest transistor feature size achievable on a silicon wafer.

Importance of Smaller Nodes

The drive to shrink process nodes is pivotal because:

- Smaller transistors fit more densely, allowing more computing power per chip area.

- Increased transistor count enables higher speeds and reduced power consumption, benefiting performance and energy efficiency.

Manufacturing Challenges

- The cost of developing new nodes skyrockets with each shrink. Equipment such as extreme ultraviolet lithography (EUV) tools is essential and costly.

- Process complexity limits manufacturing capacity to a handful of industry leaders.

- Longer development timelines slow rollout of the latest nodes.

Complementary Nature with Chiplets and 3D Packaging

Instead of using the smallest nodes for all parts of a chip, manufacturers now combine technologies:

- High-performance compute chiplets use advanced nodes (3nm or 5nm).

- Supporting chiplets use mature, cost-effective nodes.

- 3D packaging stacks these heterogeneous dies efficiently.

This synergy enables continued improvement in chip capabilities without the prohibitive cost of full-chip scaling.

For detailed industry insights, refer to: https://www.jamasoftware.com/blog/2026-predictions-for-semiconductors-ai-chiplets-and-the-path-to-sustainable-innovation/ and https://www.pragmaticsemi.com/semiconductor-technology-trends-and-predictions-2026/

The Future Outlook of New Chip Technologies: Innovation and Expansion

Synergistic Drivers of the Future

The interplay of chiplets, 3D packaging, and advanced semiconductor nodes shapes the future semiconductor landscape.

Emerging Trends

- AI-driven Electronic Design Automation (EDA): AI-powered tools reduce complexity and cost in chip design, enabling smaller companies and startups to innovate rapidly.

- Proliferation of Edge AI Chips: Increasing demand for on-device AI in IoT, consumer devices, and industrial applications drives growth of specialized low-power chips.

- Flexible and Ultra-Thin Chips: New manufacturing methods support carbon-efficient, lightweight chips suitable for next-gen form factors.

- Open Architectures and RISC-V: Open instruction sets paired with chiplet designs promote innovation and diversity beyond traditional proprietary platforms.

Learn more about AI’s role in semiconductor innovation and future tech trends: https://techcirclenow.com/latest-ai-trends-2025-updates and https://techcirclenow.com/future-of-technology-2030

Critical Sectors Impacted

These technologies will be central in powering:

- AI accelerators and data centers.

- Mobile and edge computing devices.

- Autonomous vehicles and robotics.

- Industrial IoT and smart cities.

For deeper insights into upcoming semiconductor innovations, see: https://www.pragmaticsemi.com/semiconductor-technology-trends-and-predictions-2026/ and https://blog.st.com/top-tech-trends-2026/

Conclusion: The Integrated Path Forward for New Chip Technologies

New chip technologies—including chiplets, 3D packaging, and advanced semiconductor nodes—represent the semiconductor industry’s strategic response to the slowing march of traditional transistor scaling.

- These technologies are interconnected: modular chiplets enable flexible, cost-effective designs; 3D packaging stacks functionally diverse dies vertically; and advanced nodes provide cutting-edge compute power where needed.

- Together, they enable chips that are faster, more energy-efficient, and economically viable.

- This combined approach opens innovation to a broader range of companies and applications.

As AI, edge computing, and intelligent systems become ubiquitous, understanding and tracking advancements in these new chip technologies will be essential for anyone involved in technology development, investment, or strategy.

To stay on top of broader tech innovation and industry forecasts, check out: https://techcirclenow.com/tech-predictions-2030-insights

Stay informed and ahead by following these trends—they define the future of computing.

Frequently Asked Questions

- What exactly are chiplets and why are they important?

Chiplets are smaller semiconductor dies, each specialized for a specific function, that can be integrated into a single chip package. They allow modular design, improve yields, cut costs, and enable mixed-node manufacturing, making complex chip designs more feasible and scalable.

- How does 3D packaging improve chip performance?

3D packaging stacks semiconductor dies vertically, shortening interconnect distances and improving data transfer speeds and timing. This reduces latency and power consumption while enabling smaller device form factors, which benefits mobile and edge computing applications.

- What challenges come with manufacturing at advanced semiconductor nodes?

Advanced nodes require costly and complex fabrication equipment such as EUV lithography, have longer development times, and limited manufacturing capacity restricted mainly to leading-edge foundries, making wafer production expensive and less accessible.

- How do chiplets, 3D packaging, and advanced nodes complement each other?

They create a layered approach: high-performance chiplets use advanced nodes for compute, 3D packaging stacks these varied chiplets efficiently, and mature nodes manufacture less demanding components. Together, they optimize cost, performance, power, and scalability.

- Where can I learn more about semiconductor industry trends and forecasts?

Valuable resources include Jama Software’s 2026 semiconductor predictions, Pragmatic Semiconductor’s technology trends, and STMicroelectronics’ top tech trends.

This post draws extensively on analysis from

Jama Software 2026 Semiconductor Predictions,

Pragmatic Semiconductor Technology Trends 2026, and

STMicroelectronics 2026 Top Tech Trends

Additionally, for a detailed understanding of semiconductor trends and broader context on new chip technologies, see:

https://techcirclenow.com/semiconductor-trends-driving-innovation

https://techcirclenow.com/semiconductor-manufacturing-process-explained